gem5 文档

开发

构建

使用 KVM

Sphinx 文档

Doxygen 文档

gem5 API

全系统模拟 (Full System)

内存系统

Ruby 内存系统

检查点 (Checkpoints)

定向测试器 (Directed Testers)

调试 (Debugging)

架构支持

功耗与热模型

编译工作负载

统计包 (Stats)

统计 API

Develop 分支

v19.0.0.0

v20.0.0.0

v20.0.0.2

v20.0.0.3

v20.1.0.0

v20.1.0.1

v20.1.0.5

v21.0.0.0

v21.0.1.0

v21.1.0.0

v21.1.0.1

v21.1.0.2

v21.2.0.0

v21.2.1.0

v21.2.1.1

v22.0.0.0

v22.0.0.1

v22.1.0.0

v23.0.0.0

v23.0.0.1

v24.1.0.1

gem5 标准库 (Stdlib)

gem5 资源 (Resources)

Ruby 概述

缓存一致性协议

Garnet 2.0

HeteroGarnet

MOESI CMP 目录

Garnet 合成流量

SLICC 语言

MI 示例

Garnet 独立运行

互连网络

MOESI Hammer

MOESI CMP Token

MESI 两级缓存

CHI 协议

替换策略

CPU 模型

GPU 模型

M5ops 指令

last edited: 2026-01-30 06:21:33 +0000

SimpleCPU

SimpleCPU 是一个纯粹的功能性、按序模型,适用于不需要详细模型的场景。这可能包括预热期、驱动主机的客户端系统,或者只是测试程序是否正常工作。

它最近经过重写以支持新的内存系统,现在分为三个类:

目录

BaseSimpleCPU

BaseSimpleCPU 有几个用途:

- 保存架构状态,以及 SimpleCPU 模型之间通用的统计信息。

- 定义用于检查中断、设置取指请求、处理执行前设置、处理执行后操作以及将 PC 推进到下一条指令的函数。这些函数在 SimpleCPU 模型之间也是通用的。

- 实现 ExecContext 接口。

BaseSimpleCPU 不能单独运行。您必须使用继承自 BaseSimpleCPU 的类之一,即 AtomicSimpleCPU 或 TimingSimpleCPU。

AtomicSimpleCPU

AtomicSimpleCPU 是使用原子内存访问的 SimpleCPU 版本(有关详细信息,请参阅 内存系统)。它使用原子访问的延迟估计来估计整体缓存访问时间。AtomicSimpleCPU 派生自 BaseSimpleCPU,并实现了读写内存的函数,以及 tick 函数,它定义了每个 CPU 周期发生的事情。它定义了用于连接到内存的端口,并将 CPU 连接到缓存。

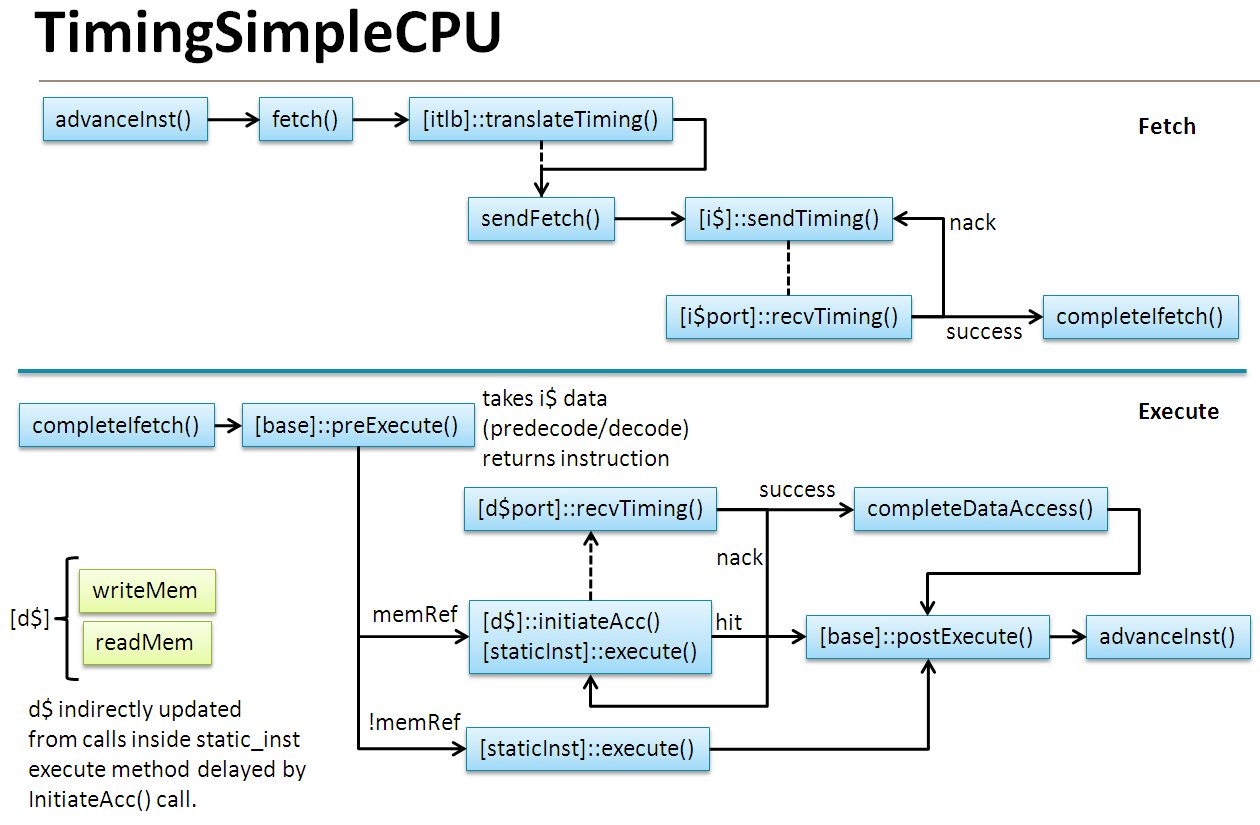

TimingSimpleCPU

TimingSimpleCPU 是使用时序内存访问的 SimpleCPU 版本(有关详细信息,请参阅 内存系统)。它在缓存访问时停顿,并在继续之前等待内存系统响应。像 AtomicSimpleCPU 一样,TimingSimpleCPU 也派生自 BaseSimpleCPU,并实现了相同的一组函数。它定义了用于连接到内存的端口,并将 CPU 连接到缓存。它还定义了处理从内存发出的访问响应的必要函数。